Earables for PCG recovery

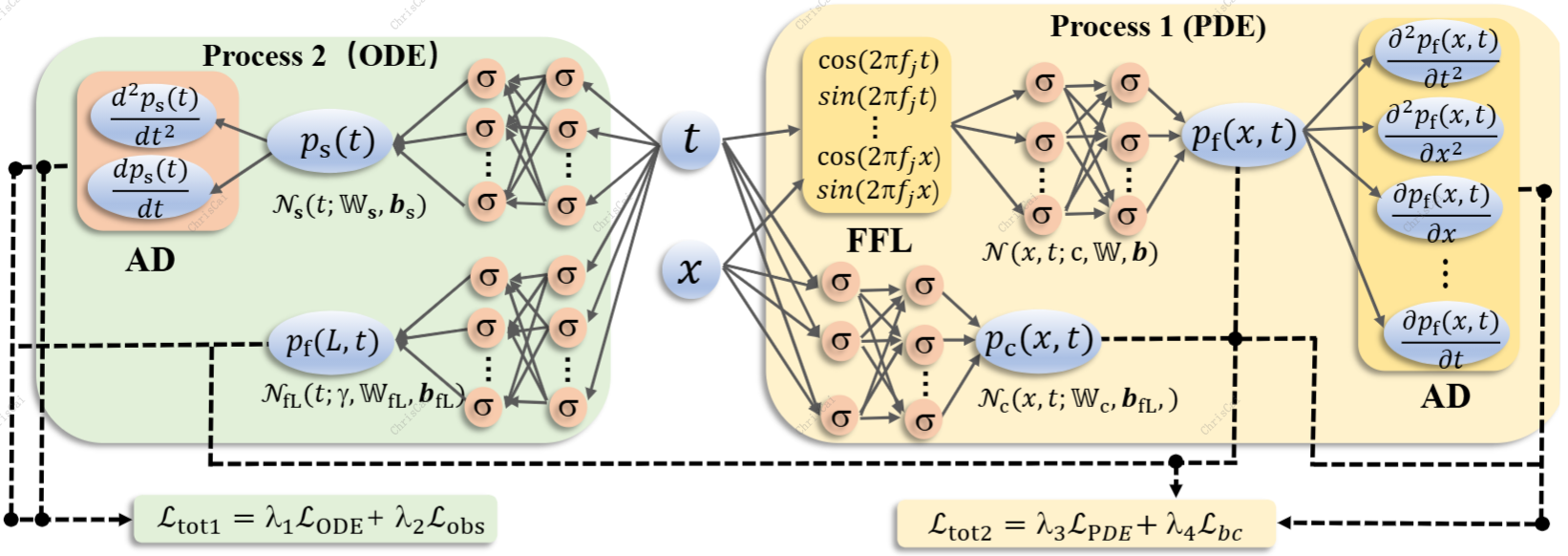

We leverage physical-informed neural network to recover PCG from in-ear sounds. We also discovery that PCG signals contain blood pressure information.

Project page

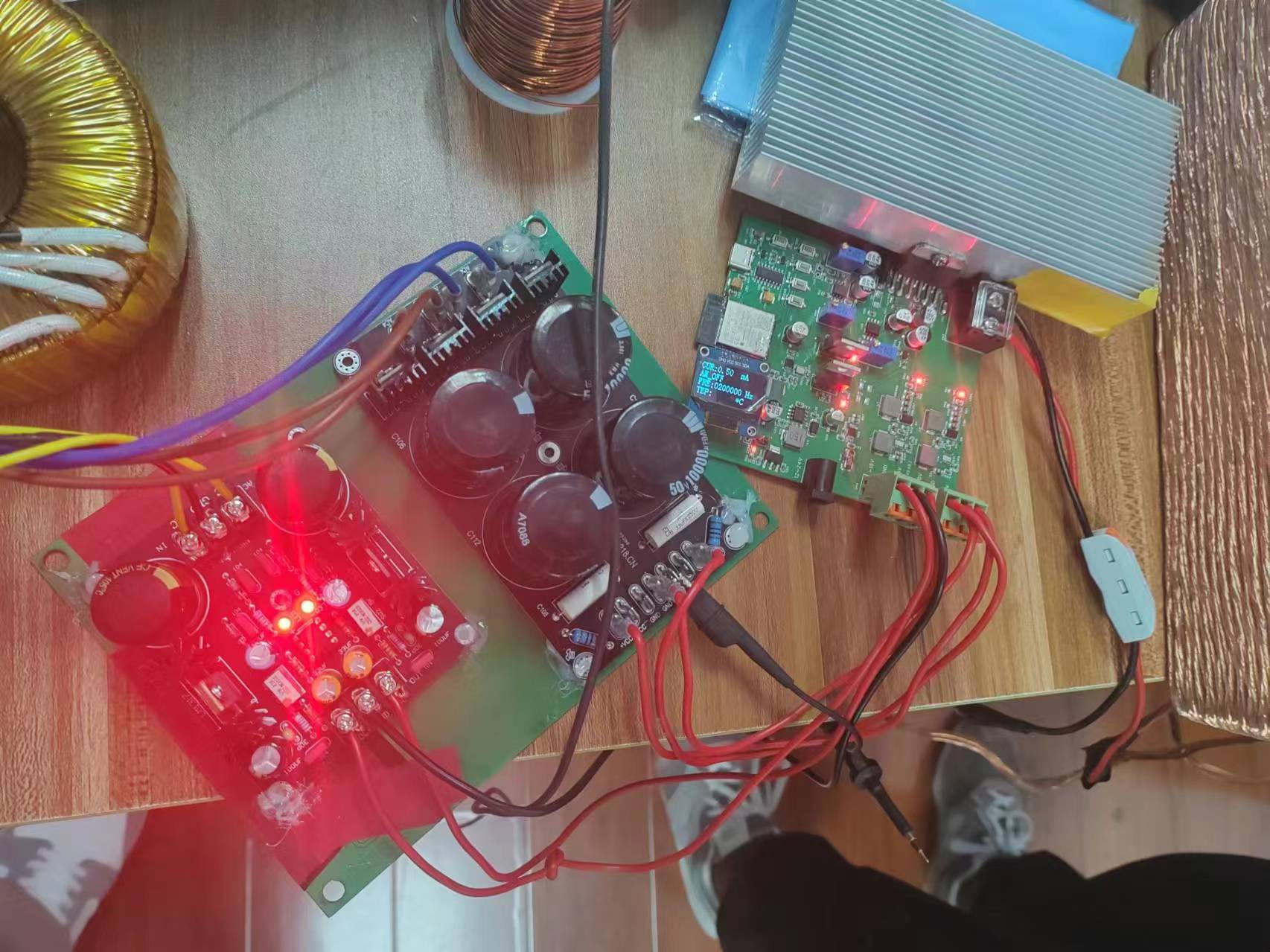

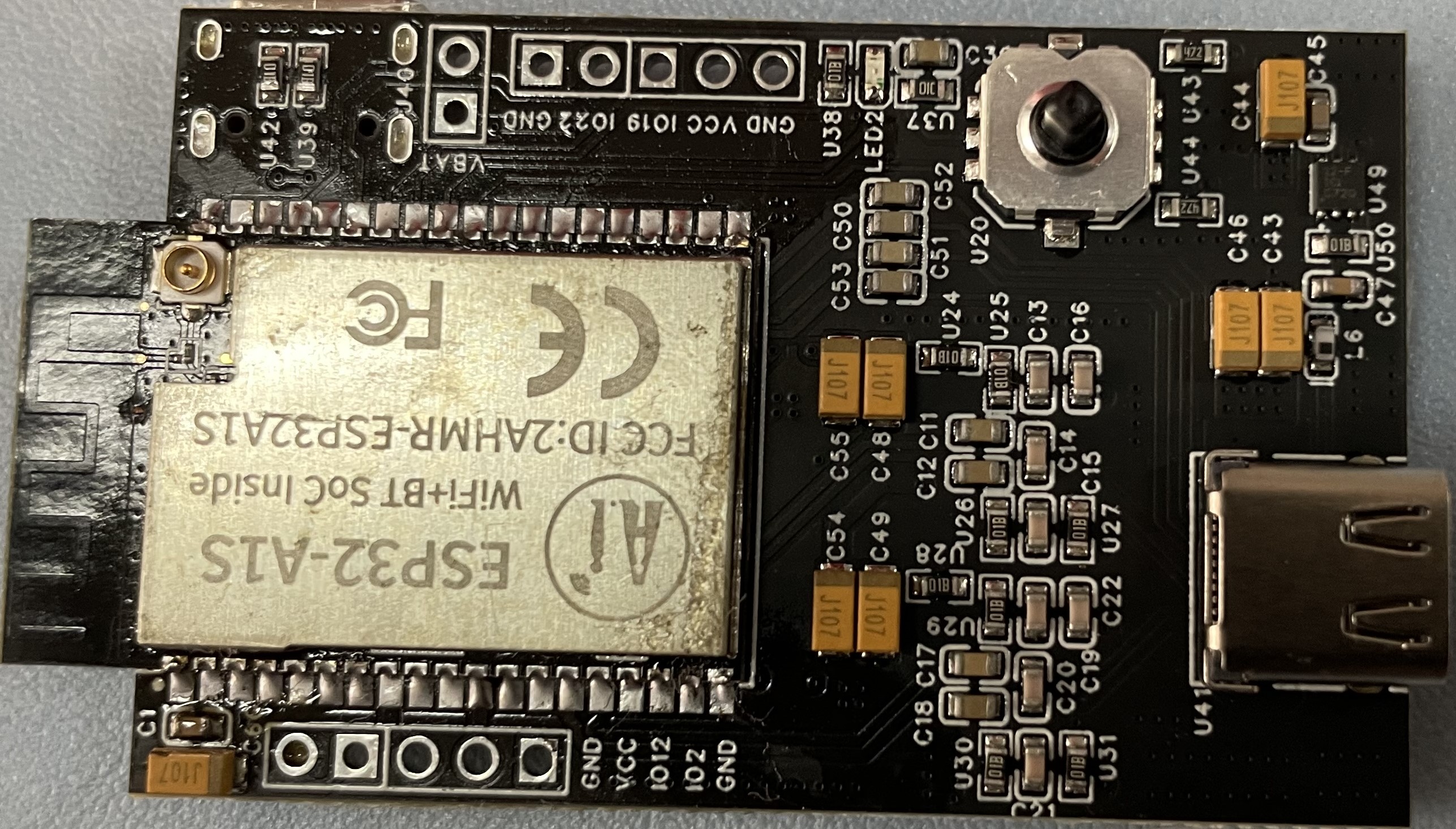

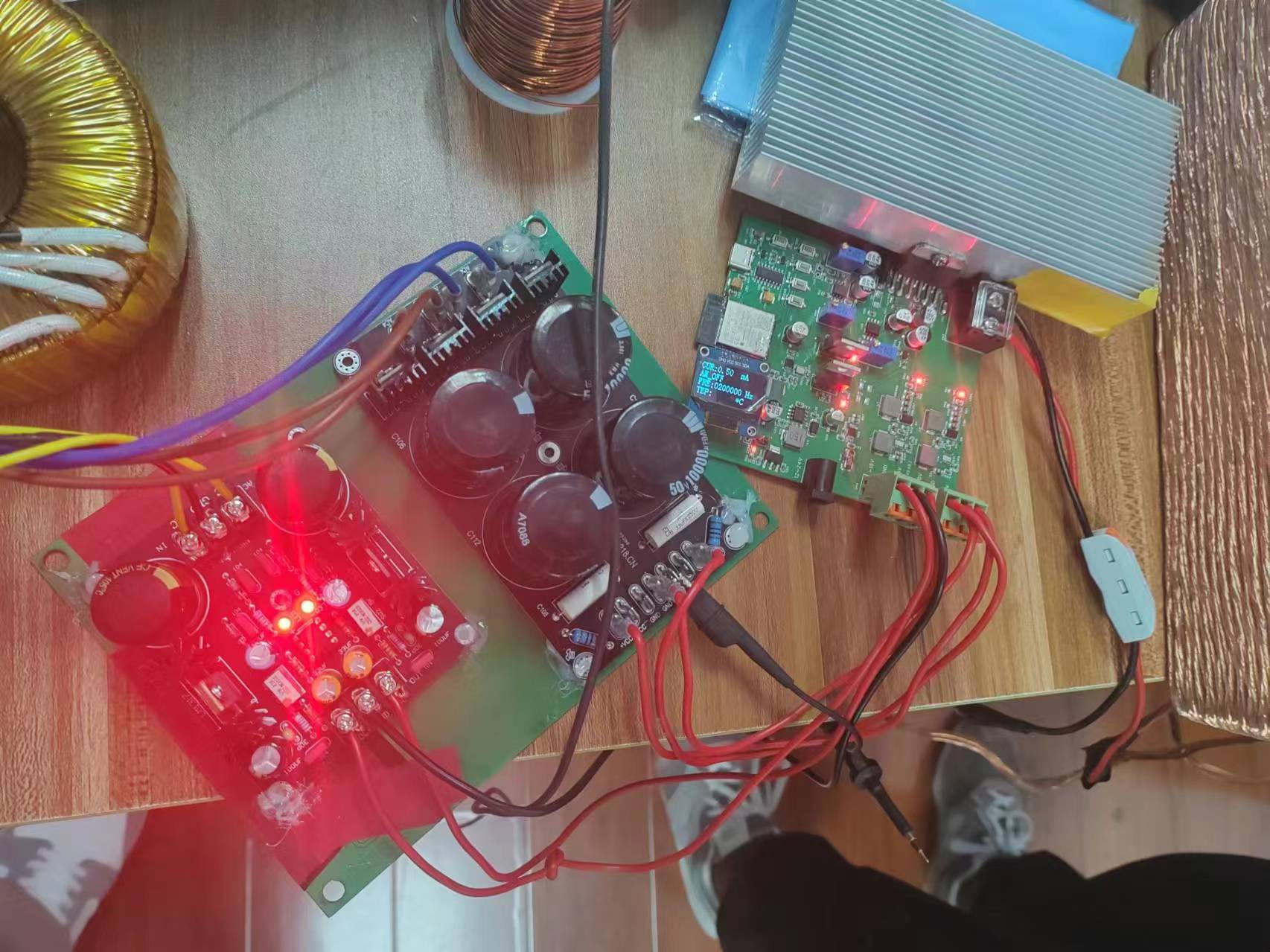

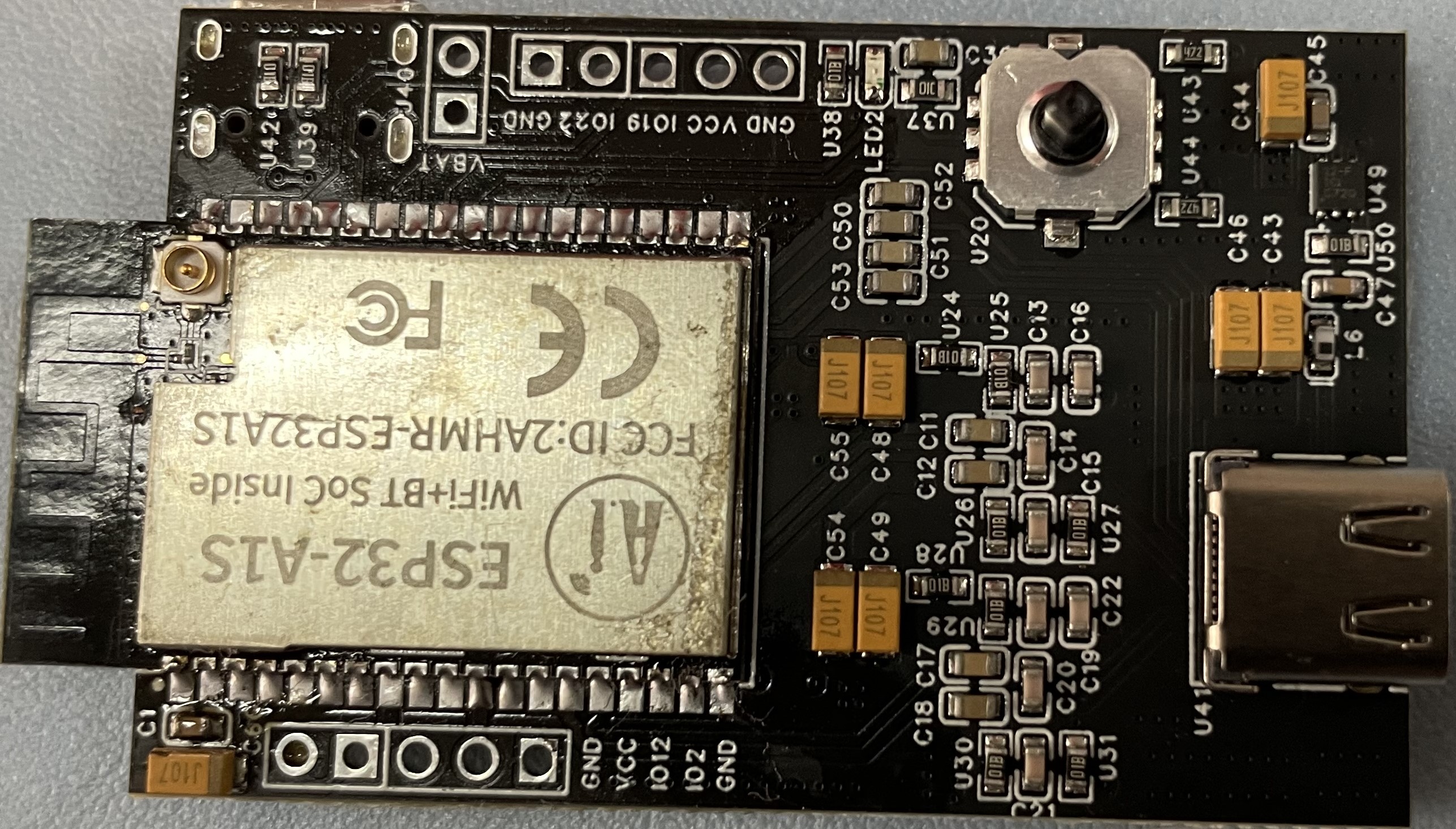

High-speed multi-channel data acquisition system

We build a 64-ch 100Ms/s data acquisition platform. It can be chained together one-by-one and used for say PET readout electronics to build dedicated algorithms to improve spatial resolution, or ultrasonic sensing to allow for spatial sampling, etc.

Project page

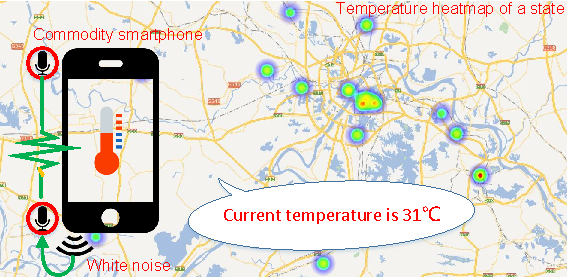

Wireless Powered Passive Temperature Tag

We build the first wirelss power temperature tag with high precision. This tag harvests energies from magnetic resonance so it is totally eco-friendly. The tag and reader can communicate with up to a distance of 50cm, and is water-proof. This system can be used for medical transportation, inhospital patient care, and many other scenarios.

Project page

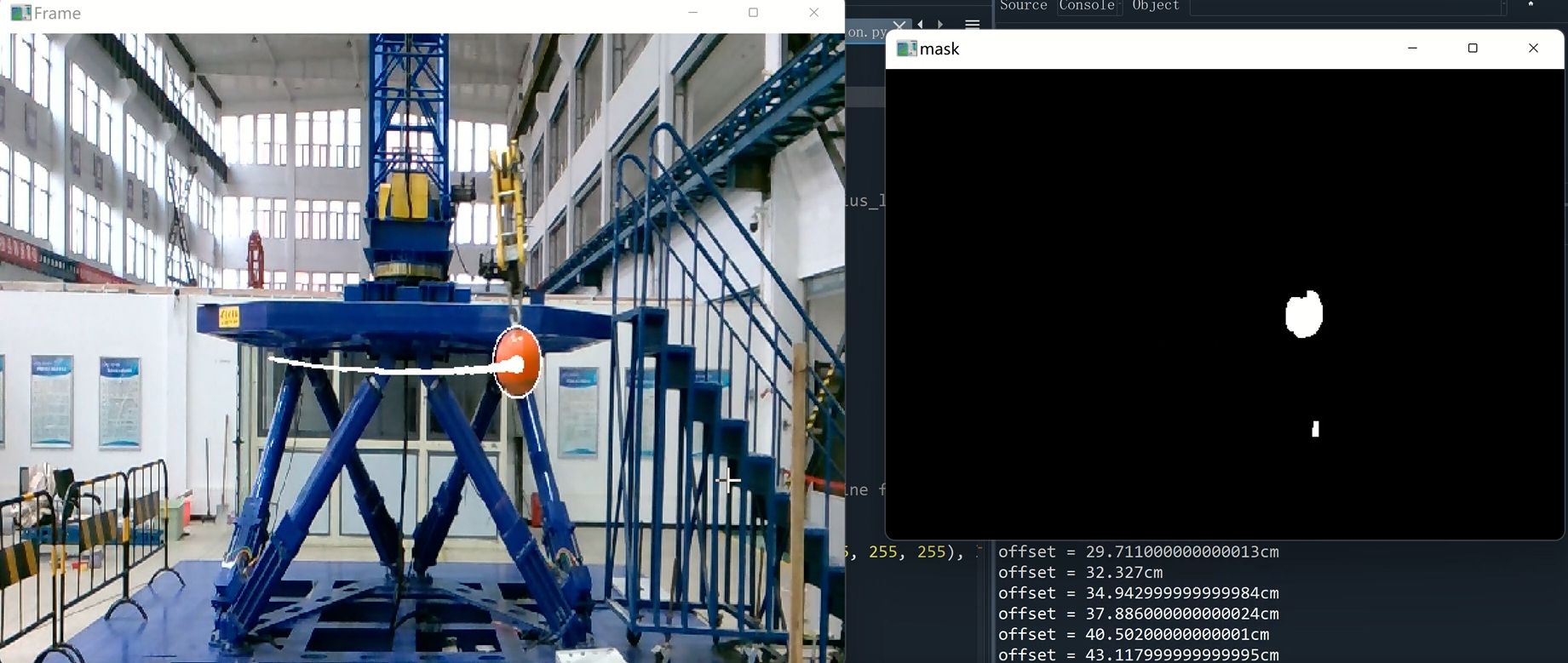

A Computer Vision based Crane Stablization System

In this project, we leverage CV techniques to track a cargo on a crane, which is used to emulate an instable board on the sea. The supporting point that load the cargo can be moved so as to mitigate the movement of the cargo, with respect to the ground.

Project page

REMVT: A Resource-efficient Energy Characterization Method

REMVT improves upone convention MVT by reducing logic resources by at least up to 75% and increasing the energy characterization resolution.

Project page

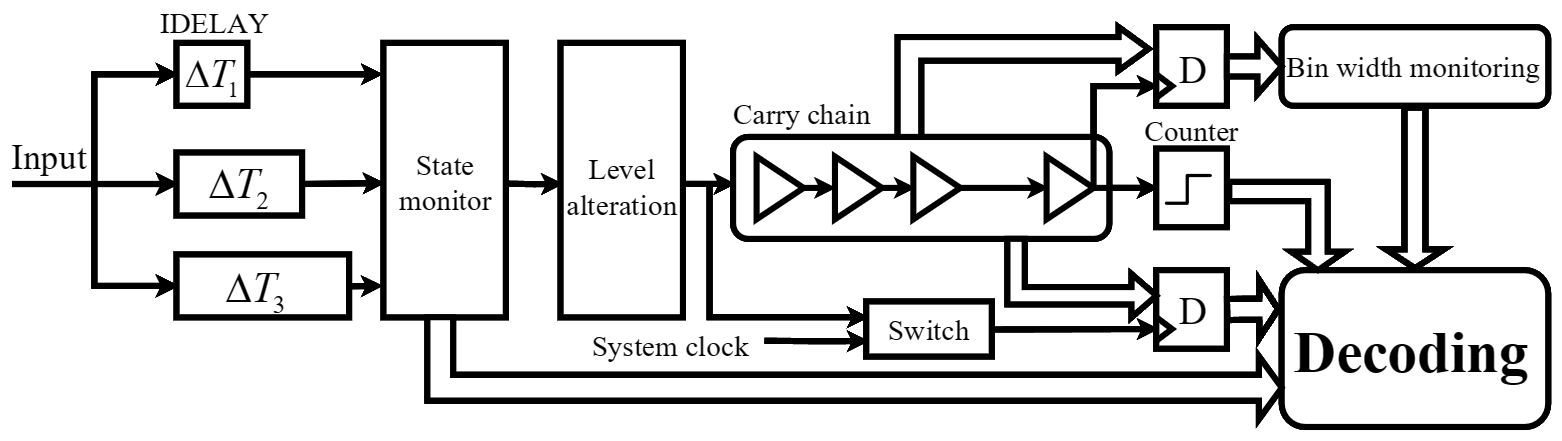

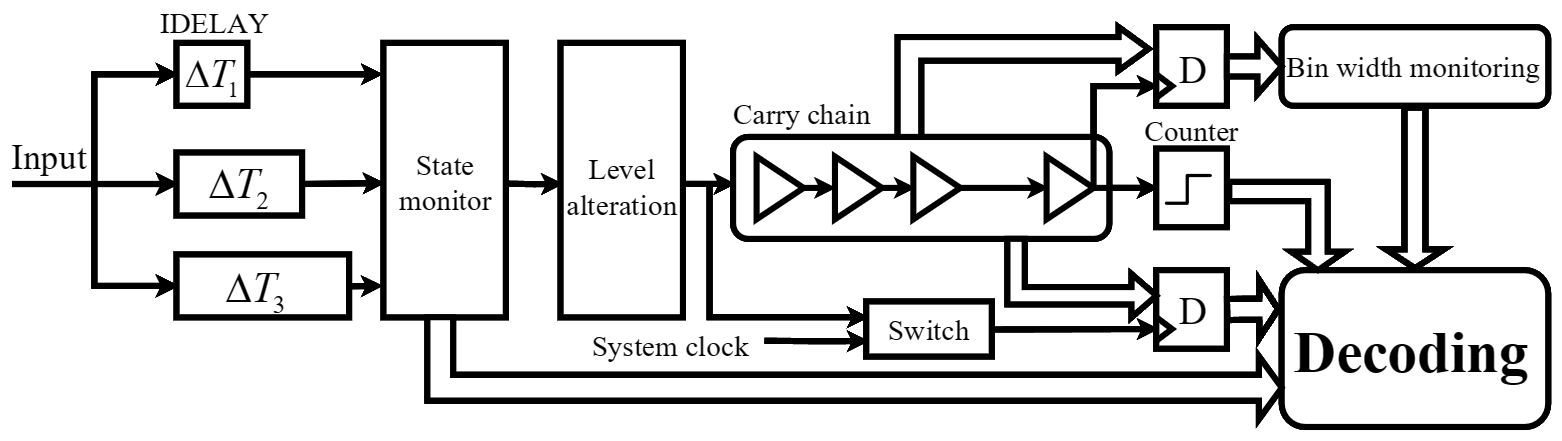

TwinPop: A Resource-efficient and Highly Linear FPGA-based Time-to-Digital Converter

TwinPop utilizes only 1/4 chain resources than conventional Tapped Delay Line (TDL) TDC, without introducing any increased dead time and even being less vulnerable to temperature fluctuations. The key technique of ToPo is a novel two-phase interpolation structure.

In this structure, we utilize few temperature-invariant delay units to imprint timestamps along a single short chain. These delay units, acting like a ring oscillator, switch respective states along the short chain if a predefined time interval is triggered, leaving decodable landmarks. Meanwhile, since only 1/4 chain resources is needed, we can constrain all logic resources within a single logic array block, significantly mitigating the nonlinearity problem, especially the ultra-wide bins.

Project page

ParCha: A New Resource-efficient and Calibration-free TDC using Parallel Short Chains

ParCha is a variant of low dead time Tapped Delay Line (TDL) TDC but we ``fold'' the long delay chain into several short parallel pieces.

The key insight here is to reallocate the measurement range of each short piece by introducing appropriate fix delay, so that they can equivalently formulate a long chain. This can effectively minimize delay cell heterogeneity, thereby eliminating the reliance on tedious calibrations. Additionally, our design utilizes less temperature-sensitive resources but relies more on temperature-invariant modules so that our design can be more resilient to temperature fluctuations. Project page

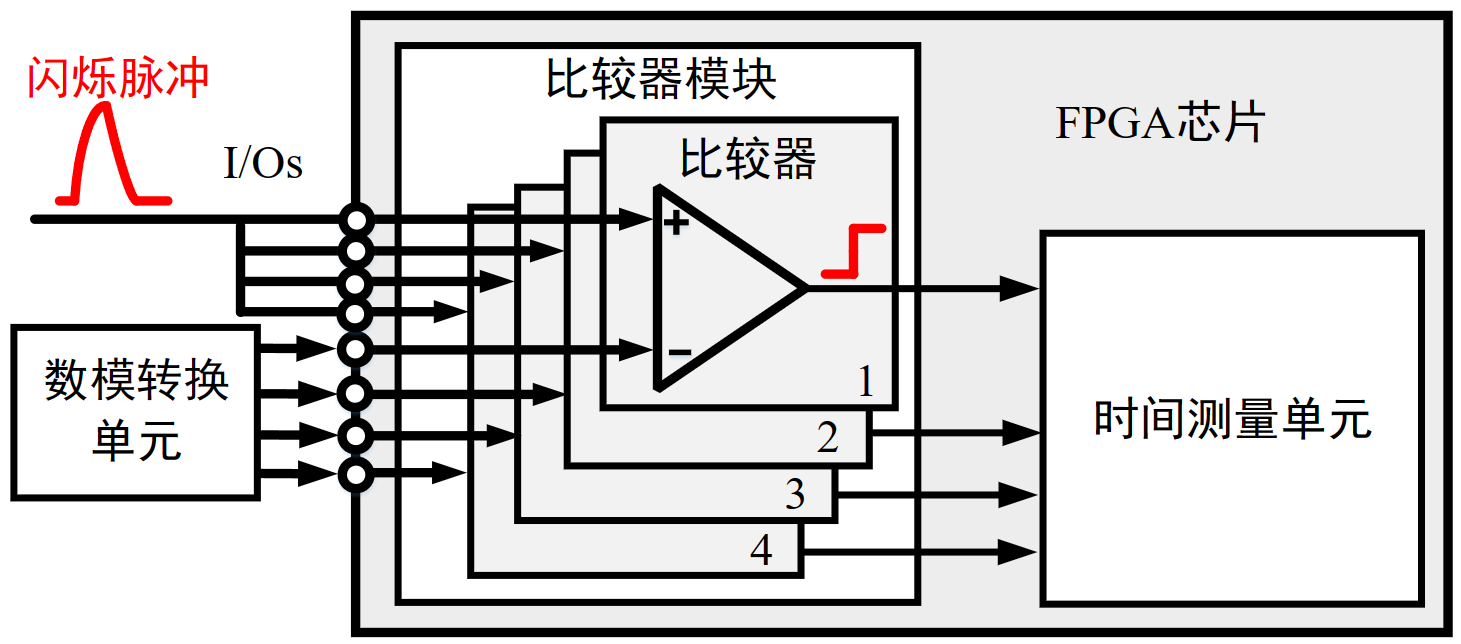

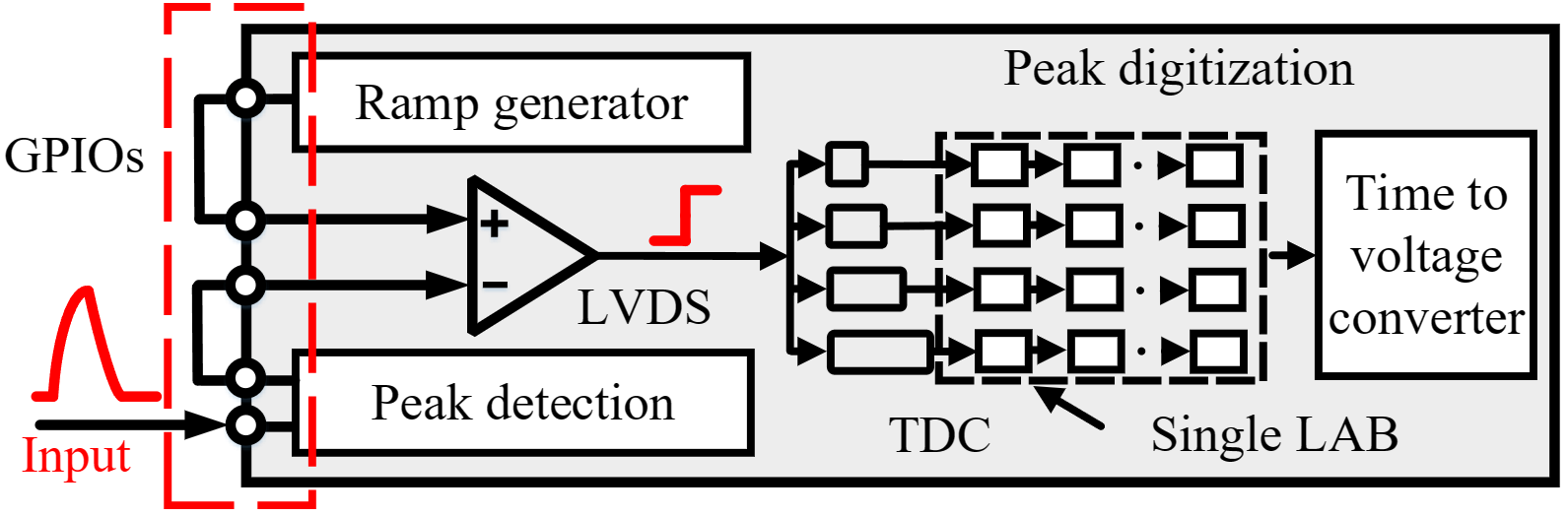

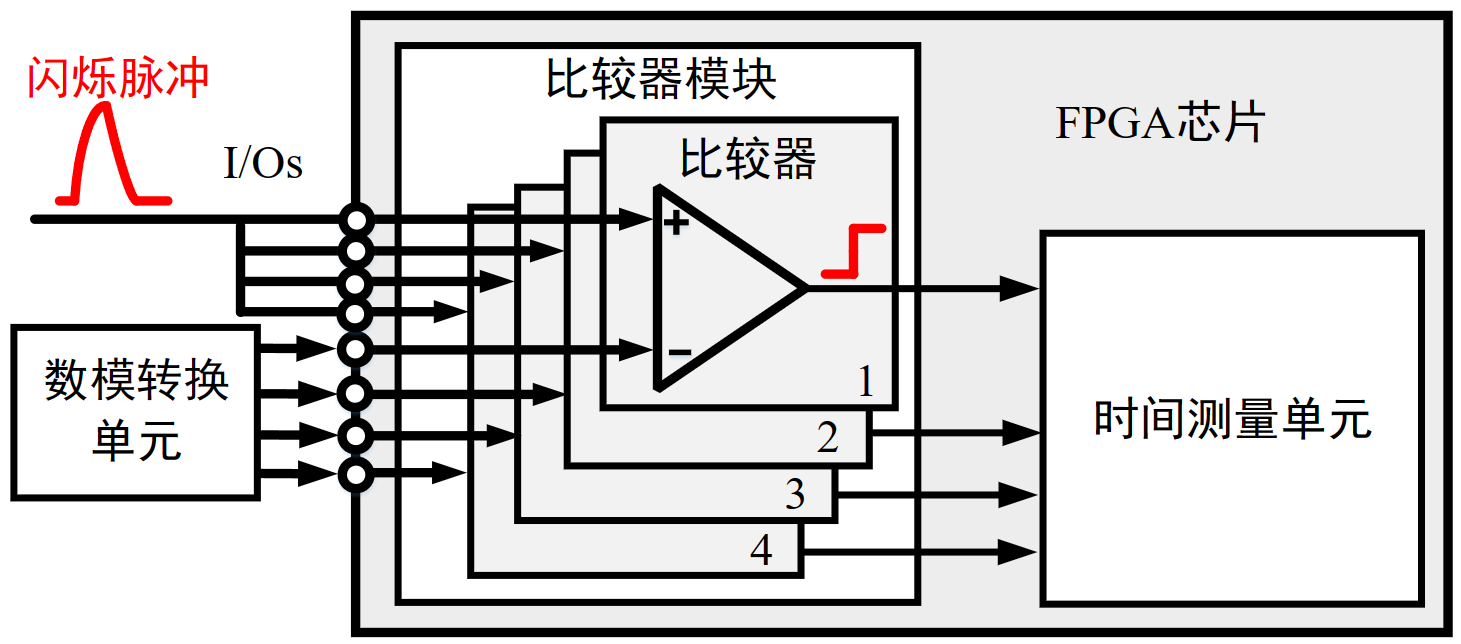

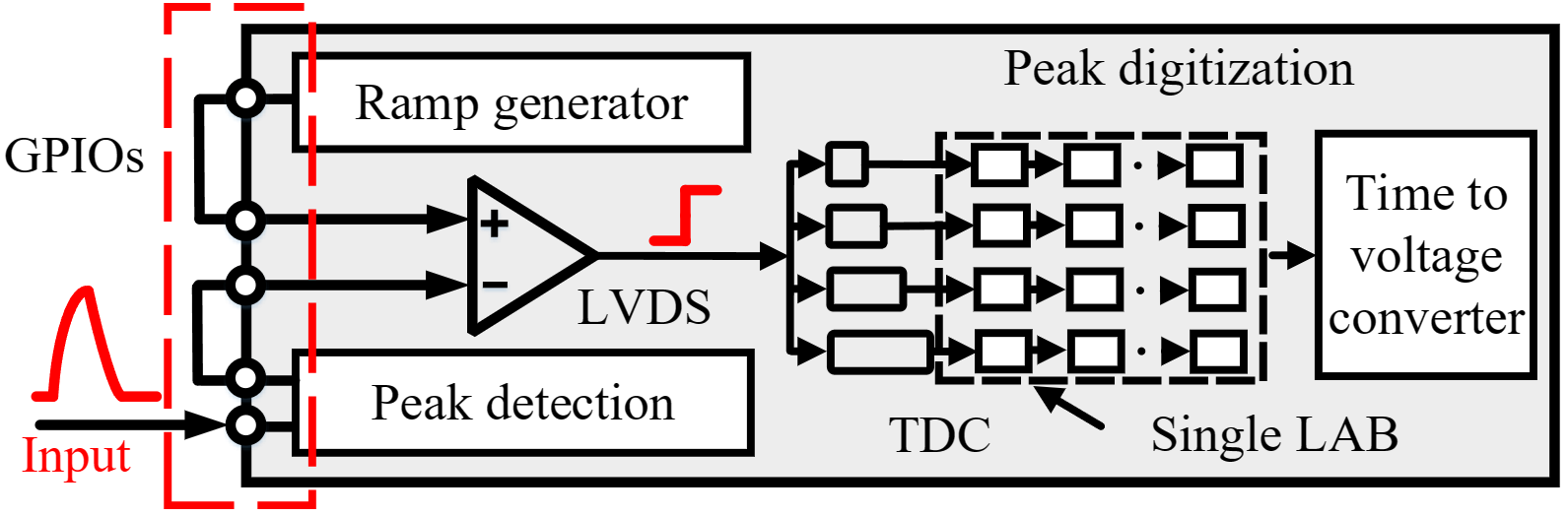

Analog Peak Detection Using Purely FPGA Solutions

We design an analog peak detection circuit using purely FPGA-only solutions. It is compact, flexible, and resource-efficient, which is appealing for multi-channel ultra-fasst signal acquisition. Project page

EarAce: Empowering Versatile Acoustic Sensing via Earable ActiveNoise Cancellation Platform

EarACE takes a compact design to handle hardware heterogeneity and to deliver flexible control on audio facilities. Leveraging a systematic study on in-ear acoustic signals, EarACE gains abilities to combat performance sensitivity to device wearing states and to eliminate body motion interference. Project page

HRCSS: Boosting Chirp Signal Based Aerial Acoustic Communication Under Dynamic Channel Conditions

HRCSS innovates in the definition of a loose orthogonality condition, and it leverages this orthogonality to overlap multiple chirp carriers in a single time duration to form a data symbol representing multiple bits, thereby substantially promoting the data rate. Project page | |